MATERI ARSITEKTUR KOMPUTER PERTEMUAN KE-12

REDUCED INSTRUCTIONS SET COMPUTER (RISC)

– Set instruksi yang terbatas dan sederhana

– Register general purpose yang berjumlah banyak, atau penggunaan teknologi kompiler untuk mengoptimalkan pemakaian registernya

– Penekanan pada pengoptimalan pipeline instruksi

1. Karakteristik karakteristik Eksekusi Instruksi

• Salah satu bentuk evolusi komputer yang paling di rasakan adalah adalah evolusi bahasa pemrograman

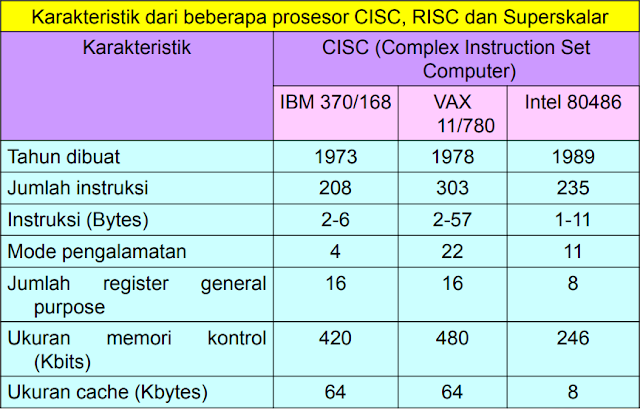

Karakteristik dari beberapa prosesor CISC, RISC dan Superskalar

Karakteristik RISC

Karakteristik Super Skalar

Aspek-aspek Komputasi

• Untuk memahami RISC harus diawali

dengan tinjauan singkat tentang

karakteristik eksekusi instruksi

• Aspek-aspek komputasi yang dimaksud

adalah sebagai berikut :

A. Operasi-operasi yang di lakukan

B. Operand-operand yang di gunakan

C. Pengurutan eksekusi

A. Operasi

B. Operand

2. Penggunaan File Register Besar

• Alasan diperlukannya penyimpanan register adalah

dengan melihat kenyataan bahwa menyimpan

register merupakan perangkat penyimpan paling

cepat, yang lebih cepat dibandingkan dengan

memori utama dan memori cache.

• File register secara fisik berukuran kecil, dan

umumnya berada pada satu keping dengan ALU

dan Control Unit dan hanya memakai alamat yang

lebih pendek dibandingkan dengan alamat-alamat

cache dan memori

• Dengan demikian, di perlukan strategi

yang dapat menjaga operand-operand

yang paling sering di akses tetap di dalam

register dan untuk meminimalkan operasioperasi register memori

• Dalam mamaksimalkan register dipakai 2

pendekatan

1. Pendekatan perangkat lunak

2. Pendekatan perangkat keras

3. Register Windows

• Penggunaan register dalam jumlah yang

besar akan mengurangi kebutuhan

mengakses memori

• Dalam hal ini tugas perancang adalah

mengatur register-register sedemikian rupa

sehingga tujuan dapat tercapai

4. File Register Berukuran Besar

VS Cache

• File register yang diorganisasikan menjadi dua

jendela, berfungsi sebagai buffer kecil yang cepat

untuk menampung subset seluruh variabel yang

memiliki kemungkinan besar akan banyak di pakai

• File register berfungsi lebih menyerupai cache

memori

• File register dapat tidak efesian dalam

menggunakan ruang, karena tidak semua prosedur

akan memerlukan ruang jendela sepenuhnya yang

telah diberikan

• File register dapat tidak efesian dalam

menggunakan ruang, karena tidak semua

prosedur akan memerlukan ruang jendela

sepenuhnya yang telah diberikan

• Sebaliknya cache memiliki ketidak efisienan

lainnya yaitu

- Data akan di baca kedalam cache dalam bentuk

blok-blok.

- sedang file register hanya berisi variabel-variabel

yang sedang di gunakan.

- Cache membaca suatu blok data, yang mungkin

sebagian darinya tidak akan di gunakanCache

memiliki kemampuan untuk menangani variabel

global dan juga variabel lokal

File Register Besar Vs Cache

5. Otimasi Register

Berbasis Kompiler

• Pada mesin RISC hanya tersedia register dalam

jumlah yang sedikit (16-32 buah)

• Disini penggunaan register yang telah di

optimalkan tersebut merupakan tenggung jawab

kompiler

• Fungsi kompiler adalah untuk menjaga operand

bagi komputasi sebanyak mungkin di dalam

register dan bukannya di dalam memori utama.

• Hal itu ditujukan untuk meminimalkan operasi load

dan store

6. Karakteristik CISC Vs RISC

• Rancangan RISC dapat memperoleh

keuntungan dengan mengambil sejumlah

feature CISC

• Rancangan CISC dapat memperoleh

keuntungan dengan mengambil sejumlah

feature RISC

Ciri-ciri RISC :

1. Instruksi berukuran tunggal

2. Ukuran yang umum adalah 4 Byte

3. Jumlah mode pengalamatan data yang

sedikit ( < 5 buah)

4. Tidak terdapat pengalamatan tak langsung

5. Tidak terdapat operasi yang

menggabungkan operasi load / store

dengan operasi aritmetika

6. Tidak terdapat lebih dari satu operand

beralamat memori per instruksi

7. Tidak mendukung perataan sembarang,

bagi data untuk operasi load/store

8. Jumlah maksimum pemakaian memori

management Unit (MMU) bagi suatu

alamat data adalah sebuah instruksi

9. Jumalh bit bagi register specifier sama

dengan lima atau lebih

10.Jumlah bit floating point register specifier

empat atau lebih

7. Kontroversi RISC dan CISC

• Tidak terdapat mesin-mesin RISC dan CISC yang

sebanding dalam hal harga, tingkat teknologi,

kompleksitas gate, kecanggihan kompiler dsb

• Tidak terdapat pengujian program yang pasti.

Kinerja bervariasi sesuai dengan programnya

• Kesulitan dalam mengumpulkan akibat-akibat yang

di sebabkan perangkat keras yang berkaitan

dengan keterampilan dalam membuat kompiler

• Kesulitan dalam mengumpulkan akibat-akibat

yang di sebabkan perangkat keras yang

berkaitan dengan keterampilan dalam membuat

kompiler

• Sebagian besar analisi komperatif tentang RISC

dilakukan pada mesin-mesin “mainan” bukannya

pada mesin-mesin komersial. Selain itu,

sebagian besar mesin yang tersedia secara

komersial dan di iklankan sebagai RISC memiliki

karakteristik campuran antara RISC dan CISC.

Dengan demikian, perbandingan yang adil

dengan mesin CISC komersial dan murni

sangatlah sulit di laksanakan

• Dalam beberapa tahun terakhir, kontroversi

RISC dangan CISC semakin berkembang.

• Hal ini disebabkan karena terjadinya semakin

konvergensinya teknologi.

• Dengan semakin bertambahnya kerapatan

keping dan semakin cepatnya perangkat keras,

maka sistem RISC menjadi semakin komplek

• Bersamaan dengan hal itu, untuk mencapai

kinerja yang maksimum, Rancangan CISC telah

di fokuskan terhadap masalah-masalah

tradisional yang berkaitan dengan RISC, seperti

misalnya pertambahan jumlah register general

purpose dan penekanan pada rancangan

pipeline instruksi

0 komentar: